#### Smart, Creative and Entrepreneurial

www.esaunggul.ac.id

#### INTERNAL MEMORY PERTEMUAN 4 BUDI TJAHJONO, S.Kom, M.Kom TEKNIK INFORMATIKA FASILKOM UEU

#### KEMAMPUAN AKHIR YANG DIHARAPKAN

- Mampu menerangkan sistem memory computer.

- Mampu memahami memory utama semikonduktor.

- Mampu memahami tentang Cache Memory

- Mengerti dan mampu menerangkan tentang komputer Pentium II and PowerPC Cache Organizations

- Mampu menerangkan tentang Advanced DRAM

Organization

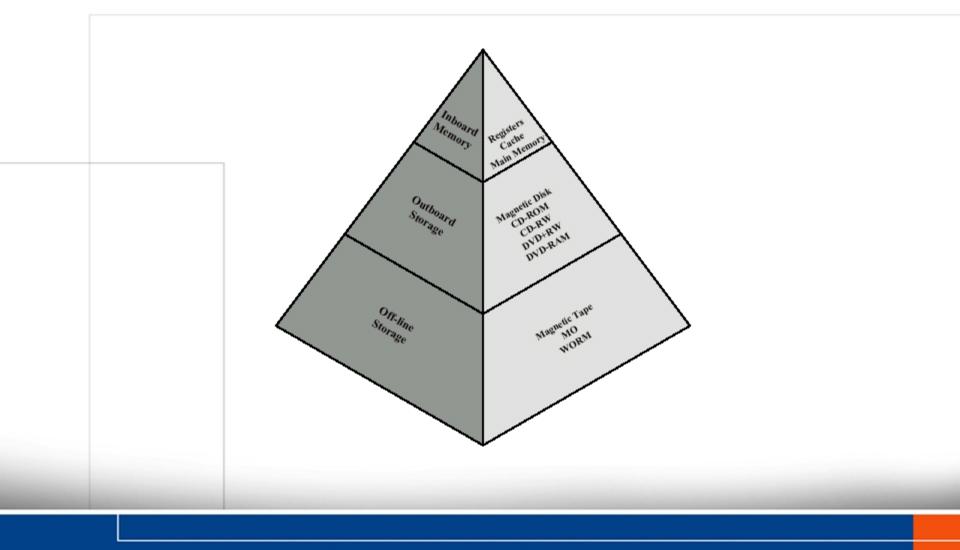

#### Memory Hierarchy

### Characteristics

- Location

- Capacity

- Unit of transfer

- Access method

- Performance

- Physical type

- Physical characteristics

- Organisation

#### Location

- CPU

- Internal

- External

#### Capacity

- Word size

- The natural unit of organisation

- Number of words

- or Bytes

# Unit of Transfer

- Internal

- Usually governed by data bus width

- External

- Usually a block which is much larger than a word

- Addressable unit

- Smallest location which can be uniquely addressed

- Word internally

- Cluster on disks

# Access Methods (1)

- Sequential

- Start at the beginning and read through in order

- Access time depends on location of data and previous location

- e.g. tape

- Direct

- Individual blocks have unique address

- Access is by jumping to vicinity plus sequential search

- Access time depends on location and previous location

# Access Methods (2)

#### Random

- Individual addresses identify locations exactly

- Access time is independent of location or previous access

- e.g. RAM

- Associative

- Data is located by a comparison with contents of a portion of the store

- Access time is independent of location or previous access

- e.g. cache

# Memory Hierarchy

- Registers

- In CPU

#### • Internal or Main memory

- May include one or more levels of cache

- "RAM"

- External memory

- Backing store

### Performance

- Access time

- Time between presenting the address and getting the valid data

- Memory Cycle time

- Time may be required for the memory to "recover" before next access

- Cycle time is access + recovery

- Transfer Rate

- Rate at which data can be moved

# **Physical Types**

- Semiconductor

- RAM

- Magnetic

- Disk & Tape

- Optical

CD & DVD

- Others

- Bubble

- Hologram

# **Physical Characteristics**

- Decay

- Volatility

- Erasable

- Power consumption

### Organisation

- Physical arrangement of bits into words

- Not always obvious

- e.g. interleaved

# Semiconductor Memory

- RAM

- Misnamed as all semiconductor memory is random access

- Read/Write

- Volatile

- Temporary storage

- Static or dynamic

### **Dynamic RAM**

- Bits stored as charge in capacitors

- Charges leak

- Need refreshing even when powered

- Simpler construction

- Smaller per bit

- Less expensive

- Need refresh circuits

- Slower

- Main memory

#### Static RAM

- Bits stored as on/off switches

- No charges to leak

- No refreshing needed when powered

- More complex construction

- Larger per bit

- More expensive

- Does not need refresh circuits

- Faster

- Cache

# Read Only Memory (ROM)

- Permanent storage

- Microprogramming (see later)

- Library subroutines

- Systems programs (BIOS)

- Function tables

# Types of ROM

- Written during manufacture

- Very expensive for small runs

- Programmable (once)

- PROM

- Needs special equipment to program

- Read "mostly"

- Erasable Programmable (EPROM)

- Erased by UV

- Electrically Erasable (EEPROM)

- Takes much longer to write than read

- Flash memory

- Erase whole memory electrically

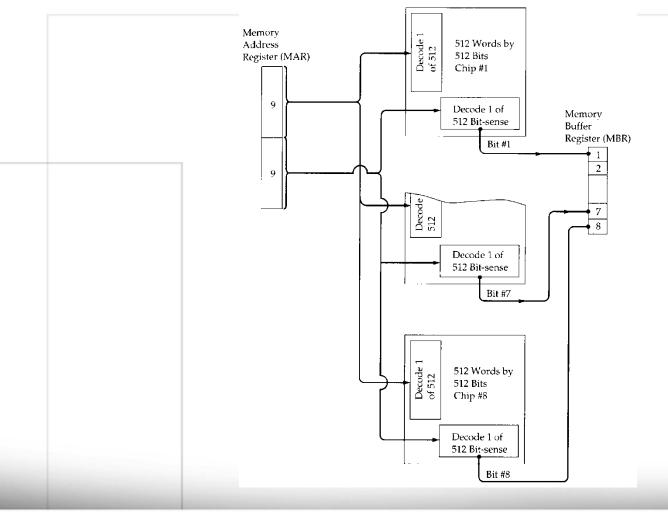

# Organisation in detail

- A 16Mbit chip can be organised as 1M of 16 bit words

- A bit per chip system has 16 lots of 1Mbit chip with bit 1 of each word in chip 1 and so on

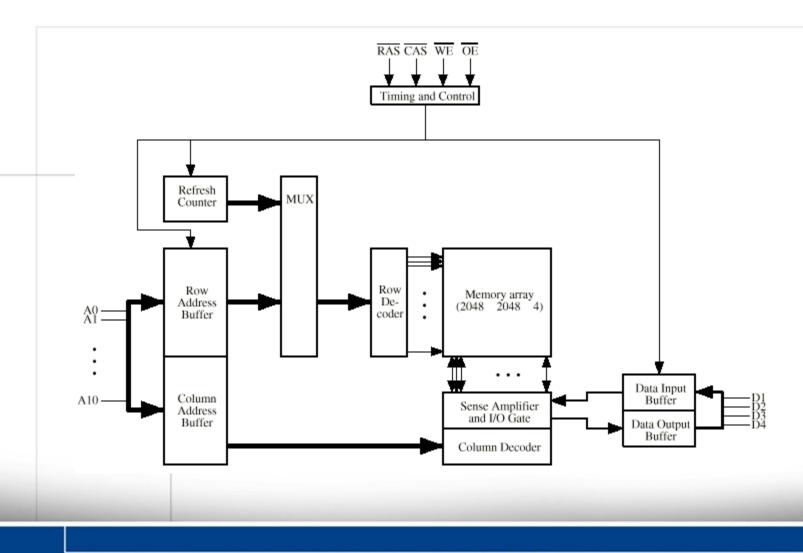

- A 16Mbit chip can be organised as a 2048 x 2048 x 4bit array

- Reduces number of address pins

- Multiplex row address and column address

- 11 pins to address (2<sup>11</sup>=2048)

- Adding one more pin doubles range of values so x4 capacity

# Typical 16 Mb DRAM (4M x 4)

# Refreshing

- Refresh circuit included on chip

- Disable chip

- Count through rows

- Read & Write back

- Takes time

- Slows down apparent performance

#### Module (256KB)

#### Organisation

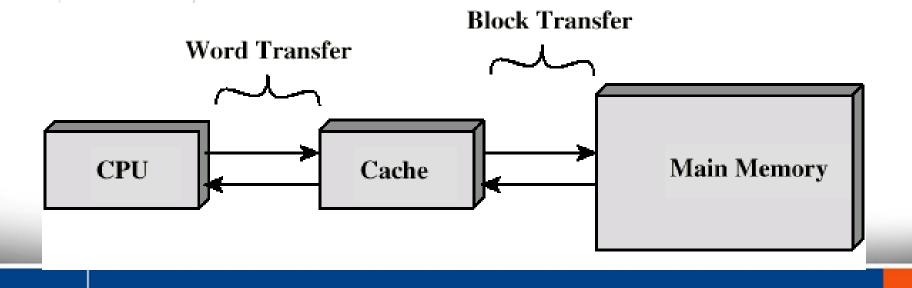

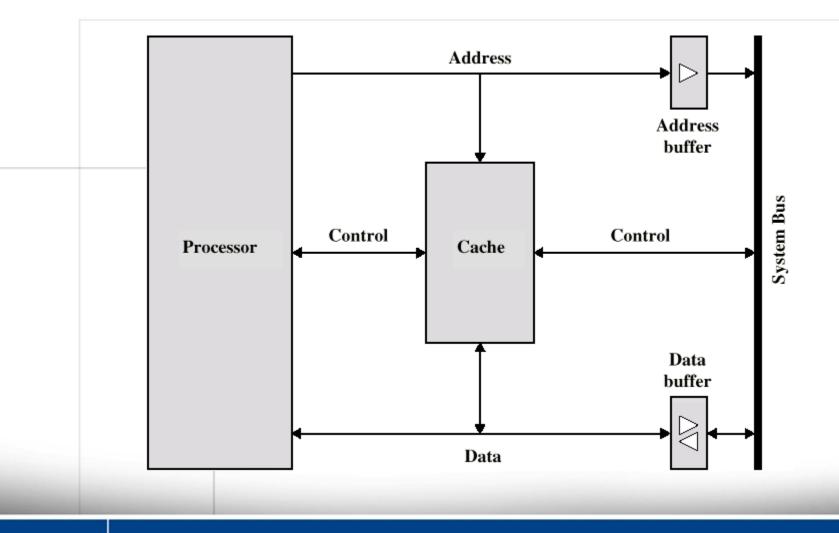

# Cache //

- Small amount of fast memory

- Sits between normal main memory and CPU

- May be located on CPU chip or module

### Cache operation - overview

- CPU requests contents of memory location

- Check cache for this data

- If present, get from cache (fast)

- If not present, read required block from main memory to cache

- Then deliver from cache to CPU

- Cache includes tags to identify which block of main memory is in each cache slot

### Size does matter

- Cost

- More cache is expensive

- Speed

- More cache is faster (up to a point)

- Checking cache for data takes time

## Typical Cache Organization //

### Cache operation - overview

- CPU requests contents of memory location

- Check cache for this data

- If present, get from cache (fast)

- If not present, read required block from main memory to cache

- Then deliver from cache to CPU

- Cache includes tags to identify which block of main memory is in each cache slot

# Cache Design

- Size

- Mapping Function

- Replacement Algorithm

- Write Policy

- Block Size

- Number of Caches

# Direct Mapping pros & cons

- Simple

- Inexpensive

- Fixed location for given block

- If a program accesses 2 blocks that map to the same line repeatedly, cache misses are very high